利用VMM建立基于事务的层次化验证平台

[10-21 14:24:02] 来源:http://www.592dz.com EDA/PLD 阅读:9351次

概要:现定向测试、随机测试、数据自检查等功能,减少了测试案例的复杂度,提高了验证生产率,减少了总的验证代码量,缩短了产品的面市时间。1基于事务的验证基于事务的验证是当前采用的主要验证技术。简单来说事务就是在接口上的操作。事务可以是抽象的和高层次的,例如可靠地发送一个TCP包,也可以是物理层面上的,例如在APB内连接上的写周期。基于事务的验证让用户不必关注底层的细节,在抽象级别更高的事务级上进行验证,从而提高了验证效率。验证环境中的组件称为事务处理器。它是一个静态的对象,它自主地生成、处理或者监视事务。传统的总线功能模型即是一种低层次的事务处理器,它将事务级激励转换成被测设计对象接口上的引脚信号跃变或者相反。而更高层次的事务处理器只有事务级接口。事务处理器根据设计对象中所使用的协议来处理事务,被测设计对象所产生的响应从引脚信号的跃变转换回事务级的响应形式。这样就可以做到在事务级上核对响应是否正确,检查出响应不相符的时候,就进一步在信号/引脚级上加以查看,从而将错误定位出来。2 VMM验证方法学VMM是一种基于 SystemVerilog的验证方法学。它最大程序地利用了 SystemVerilog的面向对象编程的优点,通过一系列机制提高了验证的生产率。2.1层次化验证模型VMM采用了易于验证重

利用VMM建立基于事务的层次化验证平台,http://www.592dz.com摘要:VMM是一种基于 SystemVerilog语言的验证方法学,它通过引入断言、抽象化、自动化与重用这四种机制提高了项目验证的生产率。本文通过一个实例介绍怎样利用 VMM建立基于事务的可重用的层次化验证平台。

0引言:

随着集成电路深亚微米时代的到来,集成电路的规模不断扩大,促进了系统级芯片 SoC(Systems-on-a-Chip)的发展和应用。通常一个 SoC芯片的规模在几百万门至几千万门左右,面对如此高的复杂度,验证成为 SoC设计中最困难、最具挑战性的课题之一。VMM(Verification Methodology Manual)验证方法学采用 SystemVerilog语言,引入了断言、抽象化、自动化及重用机制,指导验证工程师搭建基于事务的可重用的层次化验证平台,可以很容易地实现定向测试、随机测试、数据自检查等功能,减少了测试案例的复杂度,提高了验证生产率,减少了总的验证代码量,缩短了产品的面市时间。

1基于事务的验证

基于事务的验证是当前采用的主要验证技术。简单来说事务就是在接口上的操作。事务可以是抽象的和高层次的,例如可靠地发送一个TCP包,也可以是物理层面上的,例如在APB内连接上的写周期。基于事务的验证让用户不必关注底层的细节,在抽象级别更高的事务级上进行验证,从而提高了验证效率。

验证环境中的组件称为事务处理器。它是一个静态的对象,它自主地生成、处理或者监视事务。传统的总线功能模型即是一种低层次的事务处理器,它将事务级激励转换成被测设计对象接口上的引脚信号跃变或者相反。而更高层次的事务处理器只有事务级接口。事务处理器根据设计对象中所使用的协议来处理事务,被测设计对象所产生的响应从引脚信号的跃变转换回事务级的响应形式。这样就可以做到在事务级上核对响应是否正确,检查出响应不相符的时候,就进一步在信号/引脚级上加以查看,从而将错误定位出来。

2 VMM验证方法学

VMM是一种基于 SystemVerilog的验证方法学。它最大程序地利用了 SystemVerilog的面向对象编程的优点,通过一系列机制提高了验证的生产率。

2.1层次化验证模型

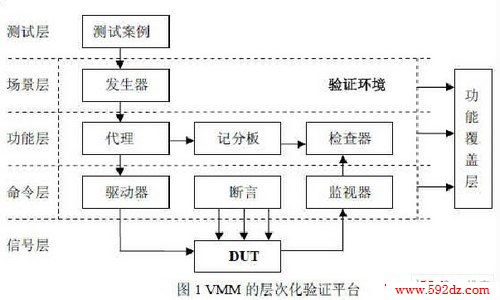

VMM采用了易于验证重用的分层式测试平台结构。每一层即建立在其他层之上的又具有一定的独立性,使得验证平台在不同的项目之间使用时,即使改变某一层的功能也不会影响其他层的重用,这样就大大提高了验证的重用性。

可以看出 VMM推荐的层次化验证平台从底至上被分成信号层、命令层、功能层、场景层以及测试层。其中的验证组件包括发生器、代理、驱动器、监视器、检查器、记分板以及断言。

信号层包括待测设计DUT与接口。命令层在信号层之上,向下通过信号层接口与待测设计相连,向上通过事务级通道与功能层通信,一般包括驱动器(Driver)、监视器(Monitor)和断言(Assertion)。驱动器将来自上层的事务转化为信号级激励输入给DUT,监视器用来监视接口信号的变化并转化为事务传递给上层的检查器。功能层位于命令层之上,是高层次操作的抽象,相互之间通过事务级通道通信。这一层主要包括代理(Agent)、检查器(Checker)和记分板(Scoreboard)。代理的作用是接收上层传来的高层事务,如DMA的读写等,并且将这些高层事务转换成单独的命令向驱动器提供。驱动器在接收到代理发出的命令后,就会生成相应的激励数据。记分板用来动态预测设计的响应,施加给DUT的激励同时施加给记分板,记分板中的转换函数把输入的激励全部转换成最后响应的形式,并保存在数据结构中,以传递给检查器,记分板还对所有的事务进行纪录与统计,记录执行的事务个数,成功失败的事务个数,是否某一事务被遗漏等。检查器通过将监视器传来的数据与记分板中存储的预测响应进行比较来判断待测功能是否正确。场景(Scenario)层在功能层之上,主要是用来生成具有一定关系的随机事务的序列。最上层是测试层,他被用来配置不同的测试案例,定义不同的约束条件。在整个验证工程中,功能覆盖率由仿真工具自动生成,测试者根据功能覆盖率来调整测试平台,修改测试案例直到覆盖率达到1O0% ,便可以认为验证过程结束。

为了充分利用SystemVerilog语言面向对象编程的优点,上述验证组件都用类(class)来实现,以提高可重用性,整个验证平台具有统一的框架,结构也变得清晰,更容易维护。

2.2 提高验证生产率的机制 VMM方法学通过 4个不同的机制提高了项目验证的生产率。这四个机制为别为 :断言、抽象化、自动化和重用。

断言是检查待测设计中信号行为是否正确的观察器,它是用描述性语言来实现的。通过在设计模块内部与其对外接口的关键位置上设置功能检查,不需要编写独立的测试代码,便能从测试平台的外观察到这些关键监视点所发生的情况,可以有效地提高观察和定位设计错误的能力。

传统的总线功能模型使的我们很难添加或结合新的协议层,而事务处理器的层次化形成了递归层次的抽象化,通过事务处理器的层次化来突破总线功能模型的限制。

在验证中, 需要产生激励来驱动设计。在时间有限的仿真过程中, 定向测试只能验证芯片的典型行为 , 而不能验证所有可能的行为, 这是定向测试的主要缺陷。而随机化激励可以仅用几行代码就能产生大量的激励数据 , 通过为设计提供随机激励信号来扩大验证的测试空间。当随机激励源不能生成所需的激励信号时,或者所需的激励不能用无侧重的随机信号源来产生时,验证者可以对随机化过程施加约束,让它生成的随机化的激励更多地落在我们感兴趣的区域或者边界内, 可更快地达到功能覆盖率的要求。

- 最新《EDA/PLD》