基于VHDL的图像传感器TCDl206的驱动设计

[10-21 14:24:02] 来源:http://www.592dz.com EDA/PLD 阅读:9730次

概要:耗低,体积小,寿命长等优点。而CCD应用的关键就是获取驱动脉冲,这里分析线阵CCD-TCDl206的工作原理和对驱动时序的要求,在此基础上设计合理的脉冲产生方案。该设计采用复杂可编程逻辑器件CPLD作为硬件设计平台,通过超高速硬件描述语言VHDL描述驱动方案,采用Altera公司的仿真软件QUARTUS II对其驱动脉冲进行仿真。1 TCDl206的主要特点TCDl206是一款高灵敏度、低暗电流、2 160像元的双沟道线阵CCD图像传感器。由2 236个PN结光电二极管构成光敏元阵列,其中前64个和后12个是用作暗电流检测而被遮蔽的,中间2 160个光电二极管是曝光像敏单元,每个光敏单元的尺寸为长14μm、高14μm,中心距亦为14μm。光敏元阵列总长为30.24 mm。TCDl206的主要特性有:1)光敏像元数为2 160像元;2)像敏单元为:14μmxl 414μm(相邻像元中心距为14μm);3)光谱范围为250~l 100 nm:4)光敏区域采用高灵敏度PN结作为光敏单元;5)时钟为二相(5 V);6)内部电路包含采样保持电路,输出预放大电路;7)采用22引脚DIP封装。2 TCDl206的结构原理和引脚功能2.1结构原理TCDl206是二相电极的双沟道线型CCD,其结构原理

基于VHDL的图像传感器TCDl206的驱动设计,http://www.592dz.com摘要:介绍图像传感器TCDl206的主要特点、结构原理、引脚功能,并详细分析其驱动时序。通过研究采用VHDL实现TCDl206驱动脉冲的方法及逻辑设计原理,完成了驱动脉冲的VHDL程序设计和时序仿真。仿真结果证明了该驱动电路的可行性。

电荷耦合器件CCD(Charge Couple Device)是集光电转换、电荷储存、电荷转移为一体的新型光电传感器件。该器件的主要功能是将光学图像转换为电信号。当对其施加特定时序脉冲时,其存储电荷能在CCD内作定向移动,从而实现自扫描.输出电压信号的大小与CCD单元存储的电荷多少成正比,CCD单元存储电荷多少与光的强度和CCD单元光积分时间成正比。与传统的光电传感器相比,CCD图像传感器具有输出噪声小,动态范围大,光谱响应范围宽,分辨率高,输出信号线性度好,功耗低,体积小,寿命长等优点。而CCD应用的关键就是获取驱动脉冲,这里分析线阵CCD-TCDl206的工作原理和对驱动时序的要求,在此基础上设计合理的脉冲产生方案。该设计采用复杂可编程逻辑器件CPLD作为硬件设计平台,通过超高速硬件描述语言VHDL描述驱动方案,采用Altera公司的仿真软件QUARTUS II对其驱动脉冲进行仿真。

1 TCDl206的主要特点

TCDl206是一款高灵敏度、低暗电流、2 160像元的双沟道线阵CCD图像传感器。由2 236个PN结光电二极管构成光敏元阵列,其中前64个和后12个是用作暗电流检测而被遮蔽的,中间2 160个光电二极管是曝光像敏单元,每个光敏单元的尺寸为长14μm、高14μm,中心距亦为14μm。光敏元阵列总长为30.24 mm。

TCDl206的主要特性有:1)光敏像元数为2 160像元;2)像敏单元为:14μmxl 414μm(相邻像元中心距为14μm);3)光谱范围为250~l 100 nm:4)光敏区域采用高灵敏度PN结作为光敏单元;5)时钟为二相(5 V);6)内部电路包含采样保持电路,输出预放大电路;7)采用22引脚DIP封装。

2 TCDl206的结构原理和引脚功能

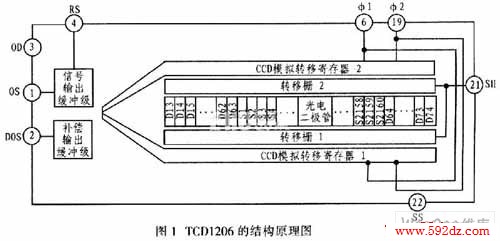

2.1结构原理

TCDl206是二相电极的双沟道线型CCD,其结构原理如图1所示。中间一排是由多个光敏二极管构成的光敏阵列,有效单元为2 160位,其作用是接收照射到CCD硅片的光,并将其转化成电荷信号,光敏元两侧是存储其电荷的MOS电容列一存储栅。MOS电容列两侧是转移栅电极SH。转移栅的两侧为CCD模拟移位寄存器,其输出部分由信号输出单元和补偿单元构成。

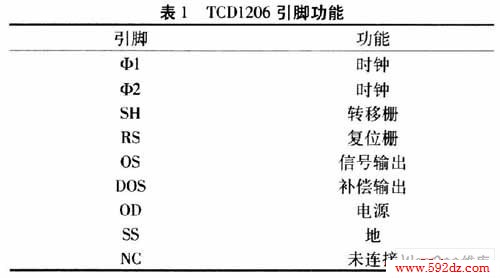

2.2引脚功能

TCDl206器件采用DIP封装,各引脚功能如表1所示。

3 驱动时序及驱动设计

3.1驱动时序分析

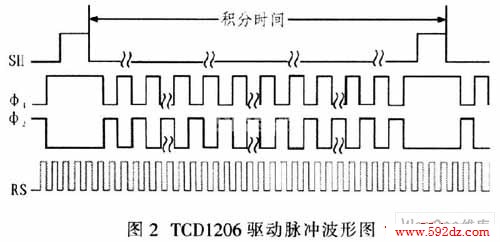

TCDl206在图2所示的驱动脉冲作用下工作。当SH脉冲高电平到来时,φ1脉冲为高电平,其下形成深势阱,同时SH的高电平使φ1电极下的深势阱与MOS电容存储势阱沟通。MOS电容中的信号电荷包通过转移栅转移到模拟移位寄存器的φ1电极下的势阱中。当φSH由高变低时,φSH低电平形成的浅势阱将存储栅下的势阱与φ1电极下的势阱隔离开。存储栅势阱进入光积分状态,而模拟移位寄存器将在φ1与φ2脉冲的作用下驱使转移到φ1电极下的势阱中的信号电荷向左转移,并经输出电路由OS电极输出。DOS端输出补偿信号。

由于结构上的安排,OS端首先输出 13个虚设单元信号,再输出51个暗信号,然后才连续输出Sl到S2160的有效像素单元信号。第S2160信号输出后,又输出9个暗信号,再输出2个奇偶检测信号,以后是空驱动。空驱动的数目可以是任意的。由于该器件是两列并行分奇偶传输的,所以在一个SH周期中至少要有1 118个φ1脉冲。RS为复位级的复位脉冲,复位一次输出一个信号。

3.2驱动电路设计

驱动电路的作用是给CCD提供正常工作所需要的逻辑时序脉冲和偏置工作电压.并在CCD的输出端把光电转换得到的电荷量转变成电压量输出。驱动脉冲信号的波形、相位、前后沿时间等对器件工作有很大影响。

为了保证CCD工作稳定可靠.必须设计符合CCD正常工作要求的时序脉冲和驱动控制电路,驱动控制脉冲与CCD良好配合,才能充分发挥CCD的光电转换、电荷存储和电荷转移等功能。不同型号的CCD要求的工作参数不同,很难设计一种驱动控制电路同时满足多种CCD工作需要,即使是相同像元数的CCD器件,若型号不同也不具有互换性。

TCDl206传感器的驱动脉冲都为周期性方波,但周期和占空比不同。其4路驱动脉冲之间需要满足特定的时序关系:根据驱动脉冲时序图可知在1个SH周期中至少有l 118个φ1脉冲。即TSH>l 118T1,T1为驱动脉冲φ1的周期。这里选择TSH=1 128T1。在SH为高电平期间,要求φ1l与φ2有一个大于SH=1持续时间的宽脉冲,这是由于此时像元中的电荷正在向两列寄存器中转移,如果在此期间φ1与φ2有上升或下降沿出现,则会造成电荷转移不完全的情况。时钟脉冲φ1,φ2频率的最大值是l MHz,典型值是0.5 MHz。复位脉冲RS频率的最大值是2 MHz,典型值是1 MHz。本设计中都选用典型值。而且φ1、φ2必须反相,占空比l:l;SH的高电平脉冲宽度要小于φ1,φ2;RS与CLK时钟的占空比为l:4。

- 最新《EDA/PLD》