FPGA实现的直接数字频率合成器

[10-21 14:57:44] 来源:http://www.592dz.com FPGA 阅读:9636次

概要:S系统的设计。2DDS的原理 DDS由相位累加器、正弦查找表、D/A转换器和低通滤波器组成,其原理如图1所示。图1中,fc为时钟频率,K为频率控制字,N为相位累加器的字长,m为ROM地址线位数,n为ROM数据线宽度(一般也为D/A转换器的位数),f0为输出频率。相位累加器由加法器和D触发器级联组成。在时钟脉冲fc的控制下,对输入频率控制字K进行累加,累加满量时产生溢出。相位累加器的输出对应于该时刻合成周期信号的相位,并且这个相位是周期性的,在0~2π范围内变化。相位累加器位数为N,最大输出为2N-1,对应于2π的相位,累加一次就输出一个相应的相位码,通过查表得到正弦信号的幅度,然后经D/A转换器转换为模拟信号,由低通滤波器滤除杂散波和谐波以后,输出一个频率为f0的正弦波。输出频率f0由fc和K共同决定。当频率控制字为K时,相位累加器的增量步长为K,经过2N/K次累加,相位累加器满量溢出,完成一个周期动作,输出频率f0与时钟频率fc之间的关系满足从而,DDS的最小频率分辨率Δfmin可达.3DDS的特点 DDS具有以下特点:(1)频率分辨率高。DDS的频率分辨率在fc固定时,取决于相位累加器的位数N,只要N足够大,理论上就可以获得相应的分辨精度,这是传统方法难以实现的。(2

FPGA实现的直接数字频率合成器,http://www.592dz.com【摘 要】 描述了直接数字频率合成器(DDS)的原理和特点,并给出了用FPGA实现DDS的方法及仿真结果。<--摘要CH(结束)←-->

<--→关键CH(开始)--> 关键词:直接数字频率合成,FPGA,波形产生

<--关键EN(结束)←-->1 引 言

随着微电子技术的发展,现场可编程门阵列(FPGA)器件得到了飞速发展。由于该器件具有工作速度快、集成度高和现场可编程的优点,因而在数字信号处理中得到了广泛应用,越来越受到硬件电路设计工程师们的青睐。直接数字频率合成(DDS)技术具有频率分辨率高、频率变换速度快、相位可连续线性变化等特点,在数字通信系统中已被广泛采用。本文基于DDS的基本原理,利用Altera公司的FPGA芯片FLEX10系列器件完成了一个DDS系统的设计。

2 DDS的原理

DDS由相位累加器、正弦查找表、D/A转换器和低通滤波器组成,其原理如图1所示。

3 DDS的特点

DDS具有以下特点:

(1)频率分辨率高。DDS的频率分辨率在fc固定时,取决于相位累加器的位数N,只要N足够大,理论上就可以获得相应的分辨精度,这是传统方法难以实现的。

(2)频率变换速度快。在DDS中,一个频率的建立时间通常取决于滤波器的带宽。影响因素为相位累加器,ROM内的工艺结构,D/A转换器及其它信号处理过程中可能产生的时延。其中,信号处理的时延与时钟周期相关。由于DDS中不要相位反馈控制,频率建立及切换快,与频率分辨率、频谱纯度相互独立,明显优于PPL。

(3)DDS中相位改变是线性过程。数字相位累加器是优良的线性数字增值发生器。因此,DDS的相位误差主要依赖于时钟的相位特性,相位误差小。另外,DDS的相位是连续变化的,形成的信号具有良好的频谱特性,这是传统的直接频率合成方法所无法实现的。

(4)输出频率范围宽。理论上,DDS输出的频率范围在0~fc/2,实际上,考虑到低通滤波器的设计,为40%fc,而FPGA的时钟频率可达到100MHz,因此,利用FPGA,可以实现输出频率范围很宽的正弦信号。

4 DDS的FPGA实现

FLEX10K是Altera公司1995年推出的产品系列,不仅在芯片上集成了1万个门,还首次集成了嵌入式存储器块,可为用户提供多达3K×8位的片内RAM,以满足存储器密集型应用的需要。

FLEX10K系列器件具有以下特点:高密度阵列嵌入式编程逻辑器件系列;0.5μmCMOSSRAM工艺制造;在线可编程;所有I/O端口有输入输出寄存器;快速有效地实现特大规模电路,包括存储器、DSP、专用算术逻辑、微处理器和微控制器等;专用进位链路,可实现快速加法器和计数器功能;专用级联链路,有效地实现高速多输入功能;内部三态总线,支持系统集成;支持多时钟系统的低时滞要求;具有JTAG边界扫描测试内建电路;3.3V或5.0V工作模式;由Altera公司的MAXPLUSII开发系统提供软件支持。

我们采用FLEX10K器件设计的DDS如图2所示。

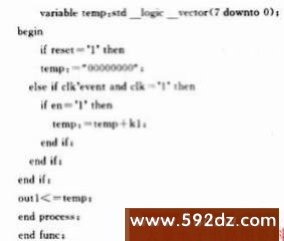

图2中,输入端K1为频率控制字,决定了DDS的频率分辨率,K2为初相控制字,clk为系统时钟,en为使能引脚,reset为复位引脚,sindata为正弦离散序列。模块SUM8×8为8位字长的相位累加器,本质上就是一个累加器,它的VHDL语言实现的主要部分如下:

- 最新《FPGA》