- ��ӭ���� - �ҾͰ������� - http://www.592dz.com ��

- |

- ���ӽ̳�

- |

- ������������

- |

- ά�̳�

- |

- ����������

- |

- |

- ����

����Ƕ��ʽLinux��TFT LCD IP�����������

[10-21 14:24:02] ��Դ��http://www.592dz.com ��Ϣ��ʾ���缼�� �Ķ���9329��

��Ҫ����Avalon Bus�Զ����г�ͻ�Ľӿ��ϼ�����Arbitrator����һ���ٲ�ģ�飬���ں�����������ʱ�䣬�û�ͨ���ı�ÿ��ģ���Ȩֵ���ı�����������ʱ��Ķ��١������ϵͳ�У�SDRAM Controller��Ӱ������ϵͳ���ܵĹؼ�����SDRAMʱ��Ƶ��Ϊ100MHz���㣬16bit��SDRAM�������ܴ���Ϊ200MByte/s��640��480��2Bytes��60Hz��TFT LCDҪռ��36MByte/s���ҵĴ���������ڻ�Ҫ������������Ĵ�������˵�Ǻܴ��Ӱ�졣LCD��������FPGAʵ��Avalon Bus Slaver�����߽ӿ�ģ��ʵ��Avalon�����߽ӿڸ���������LCD�������Ľӿڿ��ƣ�LCD������������ϵͳ����Ϊ���豸��NIOS IIͨ���ýӿڶԿ��ƼĴ����������ã�����LCD��LCD��ģ�����ĸ�32bit�Ŀɶ�д�Ĵ��������ڿ���LCD�������Ĺ�����ָʾ�乤��״̬��Avalon Bus DMA Master���豸�ӿ�ģ��ʵ��Avalon Bus DMA Master�����տ���ģ���ָ���ȡSDRAM�е����ݣ���д�뵽FIFO�У�����IJ�����DMA��ַ�ۼ���������������ʱ����ַ�ۼ�����ʼ��100MHz��ʱ������4Ϊ��λ��ʼ�ۼ��������ɶ�ȡSDRAM�ĵ�ַ������һ֡����

����Ƕ��ʽLinux��TFT LCD IP�����������,http://www.592dz.comϵͳ������Ʒ���

������ϵͳ��������ƿ�ͼ��ͼ1��ʾ��

ͼ1 ϵͳ��ͼ

����Nios II��������SDRAM�п���֡����(Frame buffer)�������ǵ�����Ҳ������˫���塣�Ե�����Ϊ������������һ֡ͼ������(640��480��2Bytes��RGB565��16bit)����֡���壬Ȼ��֡�������ַд�뵽LCD��������������LCD���������ÿ������Զ��Ӵ�������ַ����ʼ��ȡ���ݣ�������TFT�ĸ�ʽ�����ͼ�и�ģ����Avalon Bus������һ��Avalon Bus��һ�ּ����߽ṹ��Nios II�������������趼��ͨ��Avalon Bus������һ����ͼ1���Կ�������ΪSlaver��SDRAM Controller�ֱ�Ҫ�ܵ�Processor ��LCD Controller�Ŀ��ƣ�Ϊ�˽�����߳�ͻ��Avalon Bus�Զ����г�ͻ�Ľӿ��ϼ�����Arbitrator����һ���ٲ�ģ�飬���ں�����������ʱ�䣬�û�ͨ���ı�ÿ��ģ���Ȩֵ���ı�����������ʱ��Ķ��١������ϵͳ�У�SDRAM Controller��Ӱ������ϵͳ���ܵĹؼ�����SDRAMʱ��Ƶ��Ϊ100MHz���㣬16bit��SDRAM�������ܴ���Ϊ200MByte/s��640��480��2Bytes��60Hz��TFT LCDҪռ��36MByte/s���ҵĴ���������ڻ�Ҫ������������Ĵ�������˵�Ǻܴ��Ӱ�졣

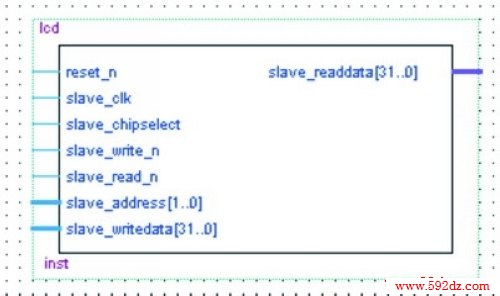

LCD��������FPGAʵ��

Avalon Bus Slaver�����߽ӿ�ģ��ʵ��

����Avalon�����߽ӿڸ���������LCD�������Ľӿڿ��ƣ�LCD������������ϵͳ����Ϊ���豸��NIOS IIͨ���ýӿڶԿ��ƼĴ����������ã�����LCD��

����LCD��ģ�����ĸ�32bit�Ŀɶ�д�Ĵ��������ڿ���LCD�������Ĺ�����ָʾ�乤��״̬��

Avalon Bus DMA Master���豸�ӿ�ģ��ʵ��

����Avalon Bus DMA Master�����տ���ģ���ָ���ȡSDRAM�е����ݣ���д�뵽FIFO�У�����IJ�����DMA��ַ�ۼ���������������ʱ����ַ�ۼ�����ʼ��100MHz��ʱ������4Ϊ��λ��ʼ�ۼ��������ɶ�ȡSDRAM�ĵ�ַ������һ֡�����ݺ��Զ���λ����ַ�������ۼӡ�

�������豸�ӿڲ��ô��ӳٵ����豸������ģʽ�������ִ���ģʽ�£���ʹû�н��յ���һ�ε���Ч���ݣ����豸Ҳ���Է�����һ�ζ������waitrequest�ź���Ч(�͵�ƽ)ʱ�����豸���������ķ���������waitrequest�ź���Ч(�ߵ�ƽ)ʱ�����豸��ʼ�ȴ���ֱ�����Ϊ�͵�ƽ����readdatavalid�ź���Ч(�ߵ�ƽ)ʱ����ʾ��������Ч����ʱ���豸�����������ݿ��ϵ���Ч���ݡ�����û��ʹ��flush�źţ�flush�źŻ����ǰ��һ��δ��ɵĶ����Avalon���߱�֤���ݵ����˳�������豸Ҫ���˳��һ��(�������豸��ַ���˳��һ��)��readdatavalid�źſ�����ΪFIFO��wrreq�źţ���������ֱ�ӽ�������������д�뵽FIFO�С���ǰ��ַ����β��ַʱ����λ�ۼ�����ʹ֮���¿�ʼ����ַ�ۼӡ���ַ�ۼ�������ģ����ͼ3��

ͼ2 LCD BSFͼ

ͼ3 �豸�ӿ�ģ��BSFͼ

FIFOģ��ʵ��

����FIFO�������Ƕ�DMA�����ͼ�����ݽ��л��棬��ƥ��ʱ�����ģ�������ٶȡ�FIFO��С�ݶ�Ϊ4096��16bit����ʵ�����ʱ���ٸ���ϵͳ��Ҫ�Լ���Դ״�������ʵ�������ԭ���ǣ���ϵͳ��Դ����������£���FIFO��С�������ô�㡣

����FIFO��DMA������д�����ݣ�д��ʱ��Ϊ100MHz����LCD��������ʱ����ģ��������ݣ�����ʱ��ΪPCLK����LCD�����ص�ɨ��Ƶ�ʣ�ͨ��ȡ25MHz���ڶ�����дʱ�ӺͶ�ʱ�������£�FIFO�����ṩrdusedw[11:0]�źţ�����ָʾFIFO���Ѿ�ʹ�õ���������ϵͳ��������һ������һ�����ޣ���FIFO�е����������������������ʱ����������ͣDMA���������DMA���䣬���Ա�֤ϵͳ���ܡ�

�����ڱ���Ӧ���У���wrclk��ϵͳʱ��(100MHz)��wrreq��master_readdatavalid��data��writedata���������DMA������д���������rdclk��12.5MHz(��ΪTFT��ʱ��Ϊ25MHz�����ݿ���Ϊ16bit����FIFO�Ŀ���Ϊ32bit��������һ���ʱ��12.5MHzȥ��ȡFIFO��Ȼ���������32bit�ĸ�16bit�͵�16bit)��rdreq��ʱ����ģ����ƣ�������ÿ��rdclk�������ض���һ�����ݵ�q��aclr��~reset_n��������ɸ�λ��������Ȼ�������źŶ���controller_GoBit�Ŀ��ơ�

����FIFO��Ʋ�����Quartus II�Դ���fifo��ģ�飬�Զ���������Ҫ��ģ�飬�����á�

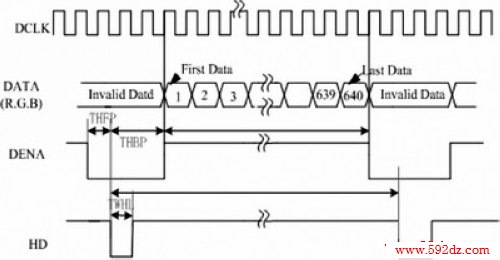

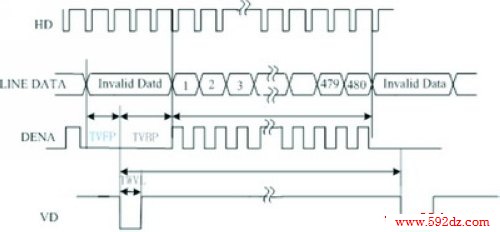

LCD ʱ���������ģ��ʵ��

����ʱ���������ڲ���TFT�����ʱ��ͼ�����ݰ��ض���ʱ�������ÿ�ֿ���������ƹؼ�����ʱ����ƣ�����ר��������˾��AA084VC05Һ������ͼ4��ͼ5����ʱ��ͼ��

ͼ4 ˮƽʱ��ͼ

- ����Ƕ��ʽLinux��TFT LCD IP�����������

- › ����Ƕ��ʽϵͳ��USB(HID)�豸

- › ����Ƕ��ʽLinux��Զ�̼��ϵͳ����Ƭجج�

- › һ�ֻ���Ƕ��ʽϵͳ��Internet��FPGA��̬���÷���

- › ����Ƕ��ʽϵͳ�ĺ��ӻ�����ϵͳ���

- › ����Ƕ��ʽuCLinux�ں��������̷��������

- › ����Ƕ��ʽϵͳ����в����ڴ涪ʧ�IJ��Է���

- › ����Ƕ��ʽϵͳ����֮�жϿ��Ƶ�ʵ��

- › ����Ƕ��ʽϵͳ��GPRSϵͳ�����

- › ����Ƕ��ʽLinux��TFT LCD IP�����������

- › ����Ƕ��ʽ��������ߴ���������ƽ̨��Ӳ��ʵ��

- › ����Ƕ��ʽ����ϵͳ�Ĵų�����ϵͳ�����

- › ����Ƕ��ʽ������Nucleus��Linux�ij�����ֲ����

- ���칦��

- ��Ƭ��ѧϰ

- ��س����

- ��ѹ��Դ

- �Զ�����

- ����������

- �ƹ���Ƶ�·

- ��·���

- PCB���

- CAD CAM

- ����ư�

- ��е�ӹ�

- ʴ����ӡ

- �Ʋ�Ϳ��

- ��·����Ƭ

- ��ҵ��

- �繤����֪ʶ

- ��������

- ��������

- ���ӻ���֪ʶ

- �������

- ��ȫ����֪ʶ

- ¥�����

- ���ӵ�

- ���ܽ���

- �ۺϲ���

- ��Ϣ��ʾ���缼��

- �ӿڶ���

- �����

- EDA/PLD

- ��������EMC

- ������

- ��·����

- ���ɵ�·

- RF��Ƶ

- armǶ��ʽ

- ��Դ����

- FPGA

- ���Ƽ���

- Ƕ��ʽϵͳ

- ģ����Ӽ���

- �������

- ���ӵ�·ͼ

- ��������

- ���¡���Ϣ��ʾ���缼����

- ���š���Ϣ��ʾ���缼����

��ϵ���� | ��վ��ͼ | ���ӽ̳� | ������������ | ά�̳� | ά����������

Copyright �ҾͰ������� All Right Reserved.