- ��ӭ���� - �ҾͰ������� - http://www.592dz.com ��

- |

- ���ӽ̳�

- |

- ������������

- |

- ά�̳�

- |

- ����������

- |

- |

- ����

����FPGA��B������ͼ��ʵʱ�ɼ�ϵͳ

[10-21 14:24:02] ��Դ��http://www.592dz.com EDA/PLD �Ķ���9446��

��Ҫ��һ����ź�ͬ����ӣ�ͬʱ�Զ��ͨ���Ļز��źŽ��пռ����ϵļӴ�������ƥ���˲�����������źŵ�����ȡ�Ȼ��Ժϳɺ�ij�����Ƶ�ź���һ��֡��ص�Ԥ��������ͼ��֡��֮֡���Ӧ���ػҶ��ϵ�ƽ����������Ϊ������ͼ���ϵ������Ƿ�����Ҿ������ֵ������������������ͬ������ȡ����֡��ƽ��ֵ������ԭͼ����ɼ�������ǿ�ȡ���֡��ع����У�FPGAҪ�������ݵĶ�ȡ�������Լ��洢����Ϊ��������Ƶ��ʾ��ʵʱ�ԣ��òɼ�ϵͳ����˫֡��ṹ��ƹ�һ��ƣ���FPGAʵ�ֶ�д�������ơ���֡��ش���������Ƶ���ݽ���д��֡��A��֡��B��֡������������ݺ�˴����ٶȶ�ȡ֡���е����ݣ�����DMA��������DMA����������DMAͨ���������ݴ��䡣FPGAʵ�ֶ�д����ʱ��Ϊ�˱���ͬʱ��һ��֡����ж�д��������Ҫ���ö�д���������д洢��״̬�л���3 ϵͳ�����ʵ��3.1 ���ֲ����ϳɶ��ھ���128��Ԫ��32�շ�ͨ���ij���̽ͷ���ڽ���32·ADת�������Ϊ4�飬ÿ��8·����ͨ����ÿ����һƬFPGAʵ�֣��ڸ�FPGA�����Ƚ��н�����ʱ�Ͷ�̬�۽��ٽ��м�Ȩ��ͣ�����ٽ���������Ͳ�������������Ƶ�źš�ÿһ���ϵͳ��ͼ��ͼ2��ʾ���Բ�ͬͨ���Ļز��źŽ��в�ͬ����ʱ�Ǵﵽ�����۽��Ĺؼ�����ʱ�����ȿɷ�Ϊ����ʱ��ϸ��ʱ������ʱ���ڿ���A��

����FPGA��B������ͼ��ʵʱ�ɼ�ϵͳ,http://www.592dz.com����1 �� ��

����ҽѧ������ϳ�������������ó�������ز�����������̽ͷ�����������������壬��������֯��������Ļز������������պ�ת��Ϊ���źţ�������ȡ���Ŵ�������������ɨ��任��ת��Ϊ����Ƶ�źţ��������ʾ��������ʾ���ڻ���FPGA+ARM 9Ӳ��ƽ̨��ȫ���ֻ�B��������У�ǰ��̽ͷ���صĻز����ź�����ʵʱ�ɼ�ϵͳ���в����ϳɡ���ش������ɼ���������ARMǶ��ʽ����ϵͳ����Ƶ�ź���������ʵʱ��Ҫ��ߣ����ѡ��FPGA+SRAM����ʵʱ�ɼ�ϵͳ�����ٶȺ������϶�����������Ҫ����Ҫ����B������ϵͳ��Ӧ��FPGA���������ƽ��г�����Ƶͼ��ɼ���ԭ����ʵ�֡�

����2 ϵͳ���ɹ���ԭ��

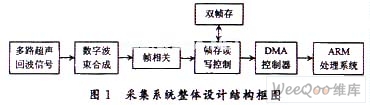

������ͼ1��ʾ���ɼ�ϵͳ���������ֲ����ϳ����Զ�ͨ�������ز��źŽ��в����ϳɣ����ֲ����ϳ����Բ�ͬͨ���źŽ�����ʱ��ʹͬһ����ź�ͬ����ӣ�ͬʱ�Զ��ͨ���Ļز��źŽ��пռ����ϵļӴ�������ƥ���˲�����������źŵ�����ȡ�Ȼ��Ժϳɺ�ij�����Ƶ�ź���һ��֡��ص�Ԥ��������ͼ��֡��֮֡���Ӧ���ػҶ��ϵ�ƽ����������Ϊ������ͼ���ϵ������Ƿ�����Ҿ������ֵ������������������ͬ������ȡ����֡��ƽ��ֵ������ԭͼ����ɼ�������ǿ�ȡ���֡��ع����У�FPGAҪ�������ݵĶ�ȡ�������Լ��洢����Ϊ��������Ƶ��ʾ��ʵʱ�ԣ��òɼ�ϵͳ����˫֡��ṹ��ƹ�һ��ƣ���FPGAʵ�ֶ�д�������ơ���֡��ش���������Ƶ���ݽ���д��֡��A��֡��B��֡������������ݺ�˴����ٶȶ�ȡ֡���е����ݣ�����DMA��������DMA����������DMAͨ���������ݴ��䡣FPGAʵ�ֶ�д����ʱ��Ϊ�˱���ͬʱ��һ��֡����ж�д��������Ҫ���ö�д���������д洢��״̬�л���

����3 ϵͳ�����ʵ��

����3.1 ���ֲ����ϳ�

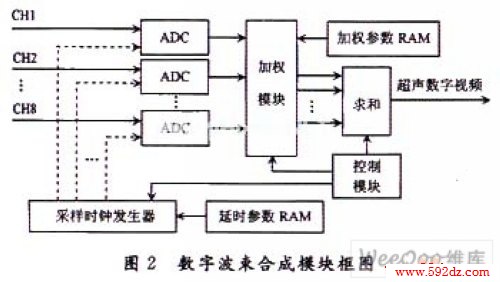

�������ھ���128��Ԫ��32�շ�ͨ���ij���̽ͷ���ڽ���32·ADת�������Ϊ4�飬ÿ��8·����ͨ����ÿ����һƬFPGAʵ�֣��ڸ�FPGA�����Ƚ��н�����ʱ�Ͷ�̬�۽��ٽ��м�Ȩ��ͣ�����ٽ���������Ͳ�������������Ƶ�źš�ÿһ���ϵͳ��ͼ��ͼ2��ʾ��

�����Բ�ͬͨ���Ļز��źŽ��в�ͬ����ʱ�Ǵﵽ�����۽��Ĺؼ�����ʱ�����ȿɷ�Ϊ����ʱ��ϸ��ʱ������ʱ���ڿ���A��D�����Ŀ�ʼʱ�䣬����Ϊ32 ns����ʱ������FPGA��Ƭ��RAM�ж���������̽ͷʱϵͳ����������Ӧ����д����ЩRAM��ϸ��ʱ�ɲ���ʱ�ӷ��������ݲ�ͬ��ͨ��������ͬ��A��D����ʱ�ӣ���Щʱ�ӵ���λ����������������ֵ�պõ��ڸ���Ԫ�����ӳ�֮����ǵ�ϵͳ��ʵʱ���Լ�̽���������ȵı仯����Ҫ���ö�̬�۽�����̬�۽�����A��D������ʼ��ͨ����ȡ��̬�۽��������ڲ����Ĺ����п��Ʋ���ʱ�ӷ�����ʵ�֡�

����8��ͨ���Ļز��źž���A��D����������FPGA������֮��ͬ�����������Ȩģ�飬��Ȩģ����8������Ϊ���ֳ˷�����ɡ��ز��źŷֱ����Ȩ������˺�õ����ж�̬�۽��ͼ�Ȩ���Ե����ݡ�8�������پ���3���ӷ����͵õ������ϳ�֮��ij���������Ƶ���ݡ�

����3.2 ֡��ش���

����֡���ģ����ͼ3��ʾ����֡��ؿ�������һƬ�洢����ɣ�����֡��صĴ洢�����ô�СΪ256 kB�ľ�̬�洢��(SRAM)��֡��ؿ�������FPGAʵ�֣���ɵ�ַ�������洢����д���ơ�֡��ؼ��㹦�ܣ���Ϊʵʱ�Ե�Ҫ����֤�������˫֡������ݲ����жϣ����Կ��ǵ�������������ݶ�д��ͬʱ�ͽ�����ش�����������Ҫ��ͬһ������ʱ����������ɡ���д��������1������ʱ�����ڵ�ǰ�����Ҫ�����洢���е����ݺ͵�ǰ֡���ݽ�����ش�����ʱ�����ڵĺ����ٽ���ش����������д��洢���Ա����ã������������˫֡���������Ȼ�Ǻ�����ʱ�Ӷ�Ӧ�������������ݡ�

����֡��صĹ����������£�

����(1)��ַ��������ַ�IJ�����һ������������ʵ�֣������ź�Ϊ֡ͬ���ź�VS������ʱ��CLK��ǰ���ṩ��֡ͬ���ź�VSΪ�ü������ĸ�λ�źţ���ÿһ֡�Ŀ�ʼ�����������㣬Ȼ���������ʱ��CLK�������ɵ�ַ��ÿ������ʱ�������ڵ�ַ���䣬���ݴ˵�ַ���д洢���Ķ�д��

����(2)��ȡ�������ݼ���ش�������һ������ʱ�����ڵ�ǰ��Σ�Ҳ����CLK����Ϊ�ߵ�ƽʱ����д����������Ķ��ź�OElΪ��Ч������ǰ֡��һ�����ص����ݣ��͵�FPGA�ڲ�ʵ�ֵļӷ�����A�ڣ���ͬʱ����B�ڵĵ�ǰ֡�Ķ�Ӧ�����������ƽ����

����(3)���ݱ��漰���䡣��ͬһ������ʱ�����ڵĺ��Σ�Ҳ����CLK����Ϊ�͵�ƽʱ����д�����������д�ź�WElΪ��Ч����ش����������д��ԭ���ĵ�ַ��ͬʱ������Ҳ����֡��д����ģ�顣

����3.3 ֡��ƹ�Ҷ�д���ƻ���

����������Ƶͼ����Ҫʵʱ�زɼ����ڴ���������ʾ�����ؽ���ͼ��洢���ͱ��벻�ϵ�д�����ݣ�ͬʱ��Ҫ���ϵشӴ洢����������������˴�������ʾ�����⣬Ϊ����������Ҫ�����ڲɼ�ϵͳ������2Ƭ����һ����֡�棬ͨ��ƹ�Ҷ�д�������������ṹ��ͼ3��ʾ��Ϊ��ȷ���κ�ʱ�̣�ֻ����1Ƭ֡�洦��д״̬������1��д��������ͬʱ��ֻ����1Ƭ֡�洦�ڶ�״̬������һ��������������ϵͳ��ʼʱ��1Ƭ֡��Ϊ�ȴ�д״̬����1ƬΪ�ȴ���״̬����ʼ������2Ƭ�����ڶ�д״̬����ת���Ĺ��̣�ת���Ĺ�����ͬ������2Ƭ״̬��������������ܹ���֤������������д��Ͷ���֡�档�û�����ͼ4��ʾ����������Ϊ��

- ����FPGA��B������ͼ��ʵʱ�ɼ�ϵͳ

- › ����FPGA��������LVDSͨ��ϵͳ���

- › ����FPGA��LCD&VGA���������

- › ����FPGA��PCI���߽ӿ����

- › ����FPGA�ĸ�Ƶʱ�ӵķ�Ƶ�ͷ������

- › ����FPGA�Ķ�����ʽ��Ƶ�������ʵ��

- › ����FPGA�Ķ���ʽ��Ƶת��ϵͳ

- › ����FPGA����������������������ʵ��

- › ����FPGA��ISD����оƬ����ƿ���

- › ����FPGA�����Ľ�ͨ�ƿ���ϵͳ���

- › ����FPGA��α�����·�������ʵ�֬�

- › ����FPGA��VGAʱ������ź�ʵ�ַ�������Ӧ��

- › ����FPGA��ֱ������Ƶ�ʺϳ�������ƺ�ʵ��

- ���칦��

- ��Ƭ��ѧϰ

- ��س����

- ��ѹ��Դ

- �Զ�����

- ����������

- �ƹ���Ƶ�·

- ��·���

- PCB���

- CAD CAM

- ����ư�

- ��е�ӹ�

- ʴ����ӡ

- �Ʋ�Ϳ��

- ��·����Ƭ

- ��ҵ��

- �繤����֪ʶ

- ��������

- ��������

- ���ӻ���֪ʶ

- �������

- ��ȫ����֪ʶ

- ¥�����

- ���ӵ�

- ���ܽ���

- �ۺϲ���

- ��Ϣ��ʾ���缼��

- �ӿڶ���

- �����

- EDA/PLD

- ��������EMC

- ������

- ��·����

- ���ɵ�·

- RF��Ƶ

- armǶ��ʽ

- ��Դ����

- FPGA

- ���Ƽ���

- Ƕ��ʽϵͳ

- ģ����Ӽ���

- �������

- ���ӵ�·ͼ

- ��������

- ���¡�EDA/PLD��

��ϵ���� | ��վ��ͼ | ���ӽ̳� | ������������ | ά�̳� | ά����������

Copyright �ҾͰ������� All Right Reserved.