- ��ӭ���� - �ҾͰ������� - http://www.592dz.com ��

- |

- ���ӽ̳�

- |

- ������������

- |

- ά�̳�

- |

- ����������

- |

- |

- ����

����FPGA����������������������ʵ��

[10-21 14:57:44] ��Դ��http://www.592dz.com FPGA �Ķ���9836��

��Ҫ����Ľ�������ȡ����ÿ��ȡ��bit������������Ĵ�����Ȼ����bit��������ڻ��Ĵ����еĻ��ֽ��бȽϣ�������һ�£������������壬����������bit����ֲ�����һ�£��������������塣����غ���������������һ��bit���ֱ����������������Ĵ��������Ĵ������ʱ��Ƶ��һ������ʱ�ӵ���ʮ������ؼ����о��ڿ�ʱ�ӵĺ����֮�ڱ�����ɡ���ˣ�ʱ����ƱȽϸ��ӣ����������ط�Ŀ��Ⱥ�խ�������ʱ�����ڣ���ϵͳ����ʱ������ɶ��塢©��Ȳ����������ϵͳ������DZ�ڵIJ��ȶ����أ���������ϵͳ���ڹ��ġ�Ϊ�ˣ��������һ����VHDL��Ƶ���FPGA������ʵ�ֵĸ���Ӳ�����������ʱ�ӣ���ʱ���㴦��������Ʒ�����3��VHDL������������ ��VHDL������������������ͼ��ͼ2��ʾ��������VHDL��Ƶ����������������һ������ʱ�ӣ������˸��ӵ�ʱ����ƣ���������ʱ���㴦����������ط�Ŀ�����һ�����ݱ��أ��Ƚ����ײ������������©��Ȳ������������������Ŀɿ��ԡ��������32��bit����������IJ���VHDLԴ����4FPGAʵ��32-bit��������������ѡ��XC4044XLA FPGAоƬʵ�֣�����������XILINX��˾��FoundationSeries3��1i���������ռ��о

����FPGA����������������������ʵ��,http://www.592dz.com��ժ��Ҫ������VHDL�����һ��32��bit��������������Ժ�ʵ��Ӧ�ñ����������ȶ��ɿ���<--ժҪCH(����)��-->

<--���ؼ�CH(��ʼ)--> �ؼ��ʣ�FPGA��VHDL�������

<--�ؼ�EN(����)��-->1��������

����ͬ����ͨ��ϵͳ��ռ�зdz���Ҫ�ĵ�λ��ͬ��ϵͳ���ܵĸߵ��ںܴ�̶��Ͼ�����ͨ��ϵͳ������������ͨ�ŵijɰܡ��������ͬ��ϵͳ�Ĺؼ�����֮һ����ˣ�Ҫ����������б������������ߵĿɿ��ԡ�ʵ��Ӧ���У��������������ʵ��Ҳ����Ӳ����·ʵ�֣����߸��ʺ��ڸ�������ͨ���е���ؼ�⡣�������ܽ�һ�������������ƵĻ����ϣ����ʵ����һ�ָ����ܵ������������

2�������������һ��ԭ��

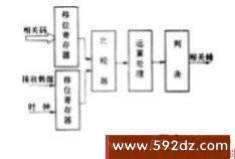

�����������һ��ԭ����ͼ1��ʾ��

�����������������������bit���ʶ�������Ľ�������ȡ����ÿ��ȡ��bit������������Ĵ�����Ȼ����bit��������ڻ��Ĵ����еĻ��ֽ��бȽϣ�������һ�£������������壬����������bit����ֲ�����һ�£��������������塣����غ���������������һ��bit���ֱ����������������Ĵ��������Ĵ������ʱ��Ƶ��һ������ʱ�ӵ���ʮ������ؼ����о��ڿ�ʱ�ӵĺ����֮�ڱ�����ɡ���ˣ�ʱ����ƱȽϸ��ӣ����������ط�Ŀ��Ⱥ�խ�������ʱ�����ڣ���ϵͳ����ʱ������ɶ��塢©��Ȳ����������ϵͳ������DZ�ڵIJ��ȶ����أ���������ϵͳ���ڹ��ġ�Ϊ�ˣ��������һ����VHDL��Ƶ���FPGA������ʵ�ֵĸ���Ӳ�����������ʱ�ӣ���ʱ���㴦��������Ʒ�����

3����VHDL������������

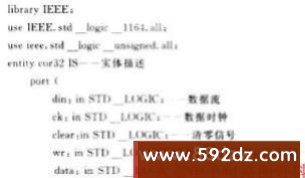

��VHDL������������������ͼ��ͼ2��ʾ��

����������VHDL��Ƶ����������������һ������ʱ�ӣ������˸��ӵ�ʱ����ƣ���������ʱ���㴦����������ط�Ŀ�����һ�����ݱ��أ��Ƚ����ײ������������©��Ȳ������������������Ŀɿ��ԡ�

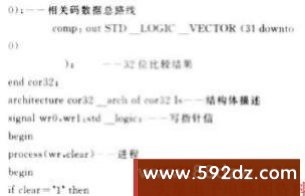

�����������32��bit����������IJ���VHDLԴ����

���������ѡ��XC4044XLA FPGAоƬʵ�֣�����������XILINX��˾��FoundationSeries3��1i���������ռ��оƬ������Դ����оƬ������ԴΪͬ��ϵͳ�������������á�

���������������������Խ���������������32λ����룺��0F7ADH��96E8H�����ɵ͵������������Ĵ����У�����������еĶ��������������ͬ�����Խ����ͼ3��ʾ��

5��������

������VHDL�����FPGAоƬ��ʵ�������������������������ӵ�����·��ƣ�������������Ĺ��ģ������������Ŀɿ��ԡ���������ѳɹ���Ӧ����ij����ͨ��ϵͳ�У������ȶ��ɿ���

�����

1����࣬���£�VHDLӲ��������������������·��ƣ��������������ӿƼ���ѧ�����磬

- ����FPGA����������������������ʵ��

- › ����FPGA��������LVDSͨ��ϵͳ���

- › ����FPGA��LCD&VGA���������

- › ����FPGA��PCI���߽ӿ����

- › ����FPGA�ĸ�Ƶʱ�ӵķ�Ƶ�ͷ������

- › ����FPGA�Ķ�����ʽ��Ƶ�������ʵ��

- › ����FPGA�Ķ���ʽ��Ƶת��ϵͳ

- › ����FPGA����������������������ʵ��

- › ����FPGA��ISD����оƬ����ƿ���

- › ����FPGA�����Ľ�ͨ�ƿ���ϵͳ���

- › ����FPGA��α�����·�������ʵ�֬�

- › ����FPGA��VGAʱ������ź�ʵ�ַ�������Ӧ��

- › ����FPGA��ֱ������Ƶ�ʺϳ�������ƺ�ʵ��

- ���칦��

- ��Ƭ��ѧϰ

- ��س����

- ��ѹ��Դ

- �Զ�����

- ����������

- �ƹ���Ƶ�·

- ��·���

- PCB���

- CAD CAM

- ����ư�

- ��е�ӹ�

- ʴ����ӡ

- �Ʋ�Ϳ��

- ��·����Ƭ

- ��ҵ��

- �繤����֪ʶ

- ��������

- ��������

- ���ӻ���֪ʶ

- �������

- ��ȫ����֪ʶ

- ¥�����

- ���ӵ�

- ���ܽ���

- �ۺϲ���

- ��Ϣ��ʾ���缼��

- �ӿڶ���

- �����

- EDA/PLD

- ��������EMC

- ������

- ��·����

- ���ɵ�·

- RF��Ƶ

- armǶ��ʽ

- ��Դ����

- FPGA

- ���Ƽ���

- Ƕ��ʽϵͳ

- ģ����Ӽ���

- �������

- ���ӵ�·ͼ

- ��������

- ���¡�FPGA��

��ϵ���� | ��վ��ͼ | ���ӽ̳� | ������������ | ά�̳� | ά����������

Copyright �ҾͰ������� All Right Reserved.