- ��ӭ���� - �ҾͰ������� - http://www.592dz.com ��

- |

- ���ӽ̳�

- |

- ������������

- |

- ά�̳�

- |

- ����������

- |

- |

- ����

����FPGA��˫��RAM��PCI9O52�ӿ����

[10-21 14:24:02] ��Դ��http://www.592dz.com EDA/PLD �Ķ���9312��

��Ҫ����״̬������д����״̬����״̬�����ڶ�����״̬ʱ����ÿ�������ز�����ADS��Ч��LW RΪ�͵�ƽ���ҷ���˫��RAM�ռ�(CS0��CSl��Ч)��״̬��ת������ʼ״̬�������Ƕ��ȴ�����״̬����ʱ����Ƭѡ�ź�CS0��CSl��ֵ���SEML��CE0L��CElL���������Ч�ĵ�ַ�Ϳ����ź�R WL��UBL��LBL��OEL��˫��RAM�������Ƕ�����״̬��Ϊ�˵õ���Ч�����ݣ��ù���δ���������������Ȼ���Ƕ����̵ȴ�״̬����ʱ����LRDY�ź���Ч�������Ч�����ݵ�PCI9052�������д����״̬���ڸù��̵���һ�����ڽ��������ź���Ϊ��Ч��״̬���ָ�Ϊ������״̬��3 FPGA����ʵ����Modelsim����ƽ̨�£�ʵ����PCI9052��д˫��RAM�ķ�����̣��÷��沨����ͼ4��ʾ���ӷ��沨�ο��Կ����ô������ʵ�ֽ�PCI90-52�Ķ�д�����ź�ת����˫��RAM�Ķ�д�����źţ����ʱ���ƥ�䡣4 ���ﱾ��Ʋ����˿ɱ����оƬ��ʵ��PCI����˫��RAM�Ľӿڵ�·���ýӿڵ�·���пɸ����������ԡ��������Ӽ����ķ�չ���ɱ�������������Ѿ��ﵽǧ���ż���Խ��Խ���ȥ������ר��оƬ������������ɵĹ������ڶ�����ͨ�����������FPGA��ʵ���ˡ�Ӳ�����������Ѿ���Ϊ������ҵ�в����赲�����ơ���һҳ [1] [2]

����FPGA��˫��RAM��PCI9O52�ӿ����,http://www.592dz.com

������ϵͳ��λ��BTERM��M S�����ߣ�LHOLD��MODE���ͣ��������ź���Ч��״̬������д����״̬��

������״̬�����ڶ�����״̬ʱ����ÿ�������ز�����ADS��Ч��LW RΪ�͵�ƽ���ҷ���˫��RAM�ռ�(CS0��CSl��Ч)��״̬��ת������ʼ״̬�������Ƕ��ȴ�����״̬����ʱ����Ƭѡ�ź�CS0��CSl��ֵ���SEML��CE0L��CElL���������Ч�ĵ�ַ�Ϳ����ź�R WL��UBL��LBL��OEL��˫��RAM�������Ƕ�����״̬��Ϊ�˵õ���Ч�����ݣ��ù���δ���������������Ȼ���Ƕ����̵ȴ�״̬����ʱ����LRDY�ź���Ч�������Ч�����ݵ�PCI9052�������д����״̬���ڸù��̵���һ�����ڽ��������ź���Ϊ��Ч��״̬���ָ�Ϊ������״̬��

����3 FPGA����ʵ��

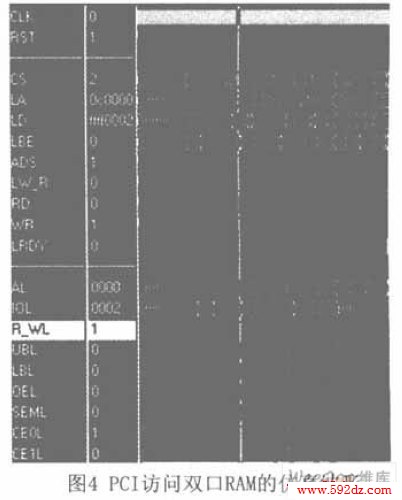

������Modelsim����ƽ̨�£�ʵ����PCI9052��д˫��RAM�ķ�����̣��÷��沨����ͼ4��ʾ���ӷ��沨�ο��Կ����ô������ʵ�ֽ�PCI90-52�Ķ�д�����ź�ת����˫��RAM�Ķ�д�����źţ����ʱ���ƥ�䡣

����4 ����

��������Ʋ����˿ɱ����оƬ��ʵ��PCI����˫��RAM�Ľӿڵ�·���ýӿڵ�·���пɸ����������ԡ��������Ӽ����ķ�չ���ɱ�������������Ѿ��ﵽǧ���ż���Խ��Խ���ȥ������ר��оƬ������������ɵĹ������ڶ�����ͨ�����������FPGA��ʵ���ˡ�Ӳ�����������Ѿ���Ϊ������ҵ�в����赲�����ơ�

- ����FPGA��˫��RAM��PCI9O52�ӿ����

- › ����FPGA��������LVDSͨ��ϵͳ���

- › ����FPGA��LCD&VGA���������

- › ����FPGA��PCI���߽ӿ����

- › ����FPGA�ĸ�Ƶʱ�ӵķ�Ƶ�ͷ������

- › ����FPGA�Ķ�����ʽ��Ƶ�������ʵ��

- › ����FPGA�Ķ���ʽ��Ƶת��ϵͳ

- › ����FPGA����������������������ʵ��

- › ����FPGA��ISD����оƬ����ƿ���

- › ����FPGA�����Ľ�ͨ�ƿ���ϵͳ���

- › ����FPGA��α�����·�������ʵ�֬�

- › ����FPGA��VGAʱ������ź�ʵ�ַ�������Ӧ��

- › ����FPGA��ֱ������Ƶ�ʺϳ�������ƺ�ʵ��

- ���칦��

- ��Ƭ��ѧϰ

- ��س����

- ��ѹ��Դ

- �Զ�����

- ����������

- �ƹ���Ƶ�·

- ��·���

- PCB���

- CAD CAM

- ����ư�

- ��е�ӹ�

- ʴ����ӡ

- �Ʋ�Ϳ��

- ��·����Ƭ

- ��ҵ��

- �繤����֪ʶ

- ��������

- ��������

- ���ӻ���֪ʶ

- �������

- ��ȫ����֪ʶ

- ¥�����

- ���ӵ�

- ���ܽ���

- �ۺϲ���

- ��Ϣ��ʾ���缼��

- �ӿڶ���

- �����

- EDA/PLD

- ��������EMC

- ������

- ��·����

- ���ɵ�·

- RF��Ƶ

- armǶ��ʽ

- ��Դ����

- FPGA

- ���Ƽ���

- Ƕ��ʽϵͳ

- ģ����Ӽ���

- �������

- ���ӵ�·ͼ

- ��������

- ���¡�EDA/PLD��

��ϵ���� | ��վ��ͼ | ���ӽ̳� | ������������ | ά�̳� | ά����������

Copyright �ҾͰ������� All Right Reserved.