- ��ӭ���� - �ҾͰ������� - http://www.592dz.com ��

- |

- ���ӽ̳�

- |

- ������������

- |

- ά�̳�

- |

- ����������

- |

- |

- ����

����FPGA��˫��RAM��PCI9O52�ӿ����

[10-21 14:24:02] ��Դ��http://www.592dz.com EDA/PLD �Ķ���9312��

��Ҫ��·���ڿɱ����������У�״̬������Ʒ�����Ӧ����㷺����Ʒ���֮һ������״̬����һ�ּ��ṹ������������ķ����������ڽ����������ά�����ر�Ӧ���ھ��д���״̬ת�ƺ���ʱ����Ƶ�ϵͳ�У����������ơ����������ƣ�����Ʋ�����Verilog HDL������״̬����ʵ�ָýӿڵ�ʱ��������ͨ�����湤����֤�˸���Ƶ���ȷ�ԡ�1 PCI9052��˫DRAM1��1 PCI9052���PCI9052��PLX��˾��PCI9050֮���ĵͼ�λ����Ŀ��ӿ�оƬ�����ģ�����PCI2��1�淶�����ľֲ�����(LOCAL BUS)����ͨ���ɱ������Ϊ8��16��32λ��(��)�������ߣ����ݴ����ʿɴﵽ132Mb��s��������Ҫ���ܺ��������£�(1)�첽������PCI9052��Local Bus��PCI���ߵ�ʱ����������У������ߵ��첽���з����˸ߡ������豸�ļ��ݡ�Local Bus������ʱ��Ƶ�ʷ�ΧΪ0��40MHz��TTL��ƽ��PCI������ʱ��Ƶ�ʷ�Χ0��33MHz��(2)�ɱ�̵ľֲ��������á�PCI9052֧��8λ��16λ��32λLocal Bus�����ǿ����Ǹ��û�Ǹ��á�PCI9052��4���ֽ�����(LBE[3��0]#)�źţ�26����ַ��(LA[27��2])���Ժ�32λ��16λ��8λ������(LAD[3l

����FPGA��˫��RAM��PCI9O52�ӿ����,http://www.592dz.com����ժҪ��Ϊ�˽��PCI9052��˫��RAM֮���дʱ��ƥ������⣬����Ʋ��ÿɱ��������ʵ������֮��Ľӿڵ�·���˵�·����ʹϵͳ���ӽ��ա����������ֲ�������״̬��ʵ�֣�ʹ������ֱ�ۼ���������Ч�ʡ�

����ͨ�����湤��ModelSim Se�Ըýӿڵ�·��������֤���ó��ķ��沨�η���Ҫ��

����O ����

����IDT70V28L(˫��RAM)�Ĵ�ȡʱ�����20ns��PCI9052������25MHz�����ȡʱ��Ҫ����˫��RAM�Ĵ�ȡʱ�䡣PCI9052�Ƿ����������ߣ��൱��һ�������������ʿ���������ͨ���ɱ������������PCI9052��д�����ź�ֱ�Ӵ��ݸ�IDT70V28L�����ʱ���ƥ�䡣

����Ϊ��PCI9052�ľֲ���ת��Ϊ˫��RAM�Ķ�д�����źź͵�ַ�źţ�����Ʋ����˿ɱ��������ʵ������֮��Ľӿ�����·���ڿɱ����������У�״̬������Ʒ�����Ӧ����㷺����Ʒ���֮һ������״̬����һ�ּ��ṹ������������ķ����������ڽ����������ά�����ر�Ӧ���ھ��д���״̬ת�ƺ���ʱ����Ƶ�ϵͳ�У����������ơ����������ƣ�����Ʋ�����Verilog HDL������״̬����ʵ�ָýӿڵ�ʱ��������ͨ�����湤����֤�˸���Ƶ���ȷ�ԡ�

����1 PCI9052��˫DRAM

����1��1 PCI9052���

����PCI9052��PLX��˾��PCI9050֮���ĵͼ�λ����Ŀ��ӿ�оƬ�����ģ�����PCI2��1�淶�����ľֲ�����(LOCAL BUS)����ͨ���ɱ������Ϊ8��16��32λ��(��)�������ߣ����ݴ����ʿɴﵽ132Mb��s��������Ҫ���ܺ��������£�

����(1)�첽������PCI9052��Local Bus��PCI���ߵ�ʱ����������У������ߵ��첽���з����˸ߡ������豸�ļ��ݡ�Local Bus������ʱ��Ƶ�ʷ�ΧΪ0��40MHz��TTL��ƽ��PCI������ʱ��Ƶ�ʷ�Χ0��33MHz��

����(2)�ɱ�̵ľֲ��������á�PCI9052֧��8λ��16λ��32λLocal Bus�����ǿ����Ǹ��û�Ǹ��á�PCI9052��4���ֽ�����(LBE[3��0]#)�źţ�26����ַ��(LA[27��2])���Ժ�32λ��16λ��8λ������(LAD[3l��0])��

����(3)ֱ�Ӵ�(Ŀ��)���ݴ���ģʽ��PCI9052֧�ִ�PCI���ߵ�Local Bus��⧷��洢��ӳ��ռ�Ĵ��ͺ�I��O���ʡ�����дFIFO������PCI�;ֲ�����֮��ĸ�����⧷���PCI���߱�����⧷�������Local Bus�ܱ����ó�⧷�����������ڡ�

����(4)4���ֲ�Ƭѡ��PCI9052�ṩ4��Ƭѡ��ÿ��Ƭѡ�Ļ���ַ�ͷ�Χ����̳ɶ�������SEEPROM��������

����(5)5���ֲ���ַ�ռ䡣ÿ���ֲ���ַ�ռ�Ļ���ַ�ͷ�Χ����SEEPROM��������̳�Ψһ�ġ�

����1��2 ˫��RAM

����IDT70V28�Ǹ���64k��16��˫�˿ھ�̬RAM�����ܱ����Ϊ1024kb��˫�˿�RAM������32λ������˫�˿�RAM����˫��RAM�ṩ���������ľ��п��ơ���ַ��I��O���ŵĶ˿ڡ�������Ҫ�������£�a����ͬʱ����˫�˿�ͬһ�洢���ռ䣻b�����ٴ洢���ʣ������ٶȿɴﵽ20ns��c���������У�d��ͬ��������豸���������Է���ؽ������߿���չ��32λ����ߣ�e�����С�busy���͡�interrupt�����������ʳ�ͻ��f�����Զ������ʶ˿ڡ�

����2 PCI��˫��RAM֮��Ľӿ����

����Ϊ�˽��PCI9052��˫��RAM֮���дʱ��ƥ������⣬���ÿɱ��������CYCLONE-II��ʵ������֮��Ľӿڵ�·�����ź����ӹ�ϵ��ͼ1��ʾ��

����PCI9052��˫��RAM������дָ������FPGA������֮�������ͨ����ѯCONF_DONE(��USERl����)��INIT_DONE(��USER3����)��ȷ��FPGA�Ƿ�������ɡ������INIT_DONE�źţ�����Ϊ�ߣ�����FPGA������ɣ������CONF_DONE������Ϊ�ߣ���PCI9052����Ҫ�ȴ�tCD2UM(min=18 ��s��max=40 ��s)ʱ����ܶ�˫��RAM���ж�д����˫��RAMʹ�õ���IDT70V28L�����Ĵ�ȡʱ�����20ns��PCI9052���÷Ǹ��á������ڶ���дģʽ��������25MHzʱ�ӣ�PCI���ʴ洢������32λλ����ÿ��д����һ����Local Bus�϶���Ӧ2��16λλ���IJ�����Ϊ�˷�ֹ���ڶ��ν��ij�ͻ��ÿ��״̬�������Լ��ADS�ź���Ч��ʼһ�ζ�д���ʣ��Ҳ���һ��NXDA�ȴ����ڡ������д����ʵ�ֹ������¡�

����2��1 PCI9052���

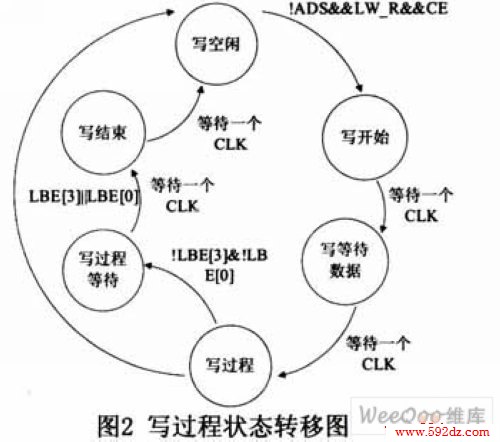

����д��������״̬��������������״̬����6��״̬���ֱ���д���С�д��ʼ��д�ȴ����ݡ�д���̡�д���̵ȴ���д�����������״̬ת��ͼ��ͼ2��ʾ��

������ϵͳ��λ��BTERM��M S�����ߣ�LHOLD��MODE���ͣ�д�����ź���Ч��״̬������д����״̬��

������״̬������д����״̬ʱ����ÿ�������ز�����ADS��Ч��LW RΪ�ߵ�ƽ���ҷ���˫��RAM�ռ�(CS0��CSl��Ч)��״̬���ͽ���д��ʼ״̬����д��ʼ״̬��״̬���ȴ�δ����һ���IJ�����������д�ȴ�����״̬����ʱ����Ƭѡ�ź�CS0��CSl��ֵ���SEML��CEOL��CElL���������Ч�ĵ�ַ�Ϳ����ź�R WL��UBL��LBL��˫��RAM��������д����״̬��Ϊ�˵õ���Ч�����ݣ��ù���δ���������������Ȼ����д���̵ȴ�״̬����ʱ����LRDY�ź���Ч�������Ч�����ݵ�˫��RAM�������д����״̬����Ƭѡ�ź�CEOI����CElL��SEMI����λ��Ч���ڸù��̵���һ�����ڽ������д�����ź���Ϊ��Ч��״̬���ָ�Ϊд����״̬��

����2��2 PCI9052������

����������Ҳ����״̬��������������״̬����6��״̬���ֱ��Ƕ����С�����ʼ�����ȴ����ݡ������̡������̵ȴ��Ͷ���������״̬ת����ͼ3��ʾ��

- ����FPGA��˫��RAM��PCI9O52�ӿ����

- › ����FPGA��������LVDSͨ��ϵͳ���

- › ����FPGA��LCD&VGA���������

- › ����FPGA��PCI���߽ӿ����

- › ����FPGA�ĸ�Ƶʱ�ӵķ�Ƶ�ͷ������

- › ����FPGA�Ķ�����ʽ��Ƶ�������ʵ��

- › ����FPGA�Ķ���ʽ��Ƶת��ϵͳ

- › ����FPGA����������������������ʵ��

- › ����FPGA��ISD����оƬ����ƿ���

- › ����FPGA�����Ľ�ͨ�ƿ���ϵͳ���

- › ����FPGA��α�����·�������ʵ�֬�

- › ����FPGA��VGAʱ������ź�ʵ�ַ�������Ӧ��

- › ����FPGA��ֱ������Ƶ�ʺϳ�������ƺ�ʵ��

- ���칦��

- ��Ƭ��ѧϰ

- ��س����

- ��ѹ��Դ

- �Զ�����

- ����������

- �ƹ���Ƶ�·

- ��·���

- PCB���

- CAD CAM

- ����ư�

- ��е�ӹ�

- ʴ����ӡ

- �Ʋ�Ϳ��

- ��·����Ƭ

- ��ҵ��

- �繤����֪ʶ

- ��������

- ��������

- ���ӻ���֪ʶ

- �������

- ��ȫ����֪ʶ

- ¥�����

- ���ӵ�

- ���ܽ���

- �ۺϲ���

- ��Ϣ��ʾ���缼��

- �ӿڶ���

- �����

- EDA/PLD

- ��������EMC

- ������

- ��·����

- ���ɵ�·

- RF��Ƶ

- armǶ��ʽ

- ��Դ����

- FPGA

- ���Ƽ���

- Ƕ��ʽϵͳ

- ģ����Ӽ���

- �������

- ���ӵ�·ͼ

- ��������

- ���¡�EDA/PLD��

��ϵ���� | ��վ��ͼ | ���ӽ̳� | ������������ | ά�̳� | ά����������

Copyright �ҾͰ������� All Right Reserved.