- ��ӭ���� - �ҾͰ������� - http://www.592dz.com ��

- |

- ���ӽ̳�

- |

- ������������

- |

- ά�̳�

- |

- ����������

- |

- |

- ����

����FPGA��Ƕ��ʽϵͳUSB�ӿ����

[10-21 14:24:02] ��Դ��http://www.592dz.com EDA/PLD �Ķ���9354��

��Ҫ��BX�ļ�ϵͳ������������PC�ķ�������ɣ��������ص������FPGAΪ���ƺ��ĵ�USB�ӿ���ơ�1 ϵͳ�ṹ��Ƹ�ϵͳͨ��TRM(Telephone Response Module)��PC������ʵ��PSTN�����Internet����֮�����ɡ���Чͨ����ͼlΪ����ϵͳ�ṹʾ��ͼ��ϵͳ�������̣���������ʱ��DAA��FPGA�����жϡ�FPGA�յ��жϺ�ʹ��USB���жϴ���������������������磬��PC��Ӧ����������ʾ�û�ѡ��ժ����ܾ���ժ����FPGA�ڽ��յ������ͻ��ͨ�绰��Ȼ����������ͨ��USB��ͬ���������˫���͡����û����Ⲧ��ʱ�������������ʱ���������ͬ�ġ�2 ϵͳӲ��ģ�����2��1ϵͳӲ����ͼ����Ʋ���FPGA��Ϊ���Ŀ�������������ƶ�����USB2��0�ӿ�����EZ-USB FX2 CY7C68013A-56��ͼ2ΪEZ-USB����������Slave FIFOģʽ��ʱFX2 USB��FPGA�ĵ��͵�·����ͼ��2��2 FPGA��USB�������еĺ��Ŀ�������FPGAѡ��Ahrea��˾��EP2C8Q208C8����USB�豸������ѡ��Cypress��˾��CY7C68013A-56��EP2C8Q208C8��Ahera Cyclone IIϵ�������е�һ�֣�Cyclone II FPGA

����FPGA��Ƕ��ʽϵͳUSB�ӿ����,http://www.592dz.com����ժҪ����ƻ���FPGA��IP-BX�绰Ӧ��ϵͳ�����ڴ�ͳ�ĵ绰����(PSTN)��PC��֮��Ľӿ����ӡ�USB2��0�ӿ�����EZ-USB FX2 CY7C68013A-56������slave FIFOģʽ��Ϊ����FPGA��Ƕ��ʽϵͳ��PC��֮���ṩ���ݺ�����ͨ�����Ӷ�������PC����FPGA֮������������ĸ��ٴ��䣬ʵ��PSTN��PC��֮��ĵ绰ͨ�š�Ӳ�����Խ������ϵͳ�����ȶ���ͨ����������Ҫ��

����ͨ�ô�������USB(Universal Serial Bus)��Ӧ����PC������ӿڼ������ѵõ��㷺Ӧ�á�USB2��0�ѳ�ΪĿǰ�����еı���չ�ӿڡ���ϵͳ��Ƶ�Ŀ������Ϊ���������绰����(PSTN)��PC��֮���ṩһ�����ֽӿڣ������PC��������������FPGA��Ƕ��ʽϵͳ��USB�豸����ϵͳ��IP-PBX�ļ�ϵͳ������������PC�ķ�������ɣ��������ص������FPGAΪ���ƺ��ĵ�USB�ӿ���ơ�

����1 ϵͳ�ṹ���

������ϵͳͨ��TRM(Telephone Response Module)��PC������ʵ��PSTN�����Internet����֮�����ɡ���Чͨ����ͼlΪ����ϵͳ�ṹʾ��ͼ��

����ϵͳ�������̣���������ʱ��DAA��FPGA�����жϡ�FPGA�յ��жϺ�ʹ��USB���жϴ���������������������磬��PC��Ӧ����������ʾ�û�ѡ��ժ����ܾ���ժ����FPGA�ڽ��յ������ͻ��ͨ�绰��Ȼ����������ͨ��USB��ͬ���������˫���͡����û����Ⲧ��ʱ�������������ʱ���������ͬ�ġ�

����2 ϵͳӲ��ģ�����

����2��1ϵͳӲ����ͼ

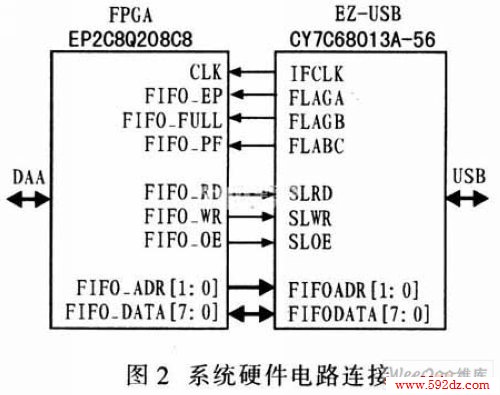

��������Ʋ���FPGA��Ϊ���Ŀ�������������ƶ�����USB2��0�ӿ�����EZ-USB FX2 CY7C68013A-56��ͼ2ΪEZ-USB����������Slave FIFOģʽ��ʱFX2 USB��FPGA�ĵ��͵�·����ͼ��

����2��2 FPGA��USB���

��������еĺ��Ŀ�������FPGAѡ��Ahrea��˾��EP2C8Q208C8����USB�豸������ѡ��Cypress��˾��CY7C68013A-56��EP2C8Q208C8��Ahera Cyclone IIϵ�������е�һ�֣�Cyclone II FPGA�ǻ���Stratix II��90 nm���������ĵͳɱ�FPGA��Cyclone II FPGA��Ӧ����Ҫ��λ���ն��г�������������ӡ����������ҵ������������EP2C8Q208C8�ڲ���2�����(PLL)��8��ȫ��ʱ�����磬8 256������Ԫ(LE)����36��M4K RAM��18���˷���ģ�飬����I��O��138����EP2C8Q208C8���еͳɱ��������ܡ����ĺͶ�IP-PBXϵͳ�Ŀ���չ��(�㹻���I��O�ӿ�)���ŵ㣬�������ѡ���������Ϊϵͳ�Ŀ���������

����CY7C68013A-56�����ǵ�1������USB2��0�ļ��������������ڲ�������1����ǿ�͵�8051��1������USB���нӿ�����(SIE)��1��USB�����շ�����3��8λ��I��O��16λ��ַ�ߡ�8��5 KB RAM��4 KB��FIFO�ȡ���ǿ��8051�ں���ȫ���805l���ݣ������ܿɴﵽ��805l��3�����ϡ�ͼ3ΪCY7C68013A-56�Ľṹ��ͼ��

����CY7C68013A���������ݴ���ʱ����4 KB��FIFO������7���˵㣺EPOIN��OUT��EPlIN��EPlOUT��EP2��EP4��EP6��EP8������EPO��EPIIN��EPlOUT��3��64 B�Ļ���˵㣬ֻ�ܱ��̼����ʣ�EP0��Ĭ�ϵ�������������˿ڻ��棬Ĭ�Ϲ����ڿ��ƴ��䣬EPlIN��EPlOUT�Ƕ�����64 B���棬�������óɿ鴫�䡢�жϴ����ͬ�����䡣�˵�2��4��6��8�Ǵ������߿��������ݴ���˵㣬������Ϊ���ִ���������ʵ�����˵�2��6�����ó�ÿ֡��512 B��l 024 B����������Ϊ2��3��4������EP2��EP6����ܱ�����Ϊ4 KB�Ļ��棻�˵�4��8��������Ϊÿ֡512 B�Ļ��档

����3 ϵͳ�������

����3��1 USB Firmware���

�������������ʹ��FPGA����USB�豸���������绰ͨ�ţ�������USB����ʹ��3��USB����ģʽ�����ƴ��䡢�жϴ��䡢��ʱ���䡣���ƴ�������ʵ���豸ö�������ı������Լ������Զ��������жϴ�������ʵ���豸�������Ļ��ѣ���Ψһ���豸�����������������ݵĴ��䷽ʽ����ʱ��������ʵ���������ݵ�˫��ͬ�����䡣USB Firmware����ص���������ͨ�ŶΡ�

����CY7C68013A����PORTS��Slave FIFO��GPlF��3�ֹ���ģʽ��PORTSģʽ������������ݴ��䷽ʽ�������ݴ�����CPUֱ�Ӳ��룬���ڴ�������Ҫ�ߵij��ϣ�GPIFģʽ��������ʽ���ڲ��������ƶ˵�FIFO��Slave FIFOģʽ�Ǵӻ���ʽ���ⲿ����������FPGA��DSP��Ӧ����ʹ���첽FIFO��ʽ�������ڲ�48 MHzʱ�ӣ��Զ���ʽ�����̼�����ı�д����Cypress��˾�ṩ�Ĺ̼�������Ϊ�����������ʼ�������������Լ������ô��롣

����������ϵͳ�У�CY7C68013A�Ĺ̼���Ҫ������¹�������ʼ��USB��������ΪUSB�ӿ�������ͨ�Ų��������ݣ�����CY7C68013A������Slave FlFO�ӿڿ���USB�������ⲿ������֮������ݴ��䡣���ͬ��������Ƚϸ��ӣ����������TD_lnit()��ʼ���⣬����Ҫ�����������������ṹ��Լ�����3�����̣�USB�������ij�ʼ�����������������������豸����Ĵ��룻�жϴ������������������жϵij�����롣ͼ4Ϊͬ�����������̡�

- ����FPGA��Ƕ��ʽϵͳUSB�ӿ����

- › ����FPGA��������LVDSͨ��ϵͳ���

- › ����FPGA��LCD&VGA���������

- › ����FPGA��PCI���߽ӿ����

- › ����FPGA�ĸ�Ƶʱ�ӵķ�Ƶ�ͷ������

- › ����FPGA�Ķ�����ʽ��Ƶ�������ʵ��

- › ����FPGA�Ķ���ʽ��Ƶת��ϵͳ

- › ����FPGA����������������������ʵ��

- › ����FPGA��ISD����оƬ����ƿ���

- › ����FPGA�����Ľ�ͨ�ƿ���ϵͳ���

- › ����FPGA��α�����·�������ʵ�֬�

- › ����FPGA��VGAʱ������ź�ʵ�ַ�������Ӧ��

- › ����FPGA��ֱ������Ƶ�ʺϳ�������ƺ�ʵ��

- ���칦��

- ��Ƭ��ѧϰ

- ��س����

- ��ѹ��Դ

- �Զ�����

- ����������

- �ƹ���Ƶ�·

- ��·���

- PCB���

- CAD CAM

- ����ư�

- ��е�ӹ�

- ʴ����ӡ

- �Ʋ�Ϳ��

- ��·����Ƭ

- ��ҵ��

- �繤����֪ʶ

- ��������

- ��������

- ���ӻ���֪ʶ

- �������

- ��ȫ����֪ʶ

- ¥�����

- ���ӵ�

- ���ܽ���

- �ۺϲ���

- ��Ϣ��ʾ���缼��

- �ӿڶ���

- �����

- EDA/PLD

- ��������EMC

- ������

- ��·����

- ���ɵ�·

- RF��Ƶ

- armǶ��ʽ

- ��Դ����

- FPGA

- ���Ƽ���

- Ƕ��ʽϵͳ

- ģ����Ӽ���

- �������

- ���ӵ�·ͼ

- ��������

- ���¡�EDA/PLD��

��ϵ���� | ��վ��ͼ | ���ӽ̳� | ������������ | ά�̳� | ά����������

Copyright �ҾͰ������� All Right Reserved.